21

4.2.5 奇偶校验模块 23

4.2.6 锁存模块 25

5 系统设计仿真 26

5.1 Quartus II仿真设置过程 26

5.2 Quartus II仿真结果 28

5.3 PCI测试结果 30

5.4 Quartus II仿真过程中出现的错误 31

6 总 结 32

致谢 34

参考文献 35

1 引言

1.1 本文的研究背景

随着微处理器、多媒体技术以及网络技术的不断发展壮大,我们对计算机I/O接口的性能要求越来越高,不断提出新的技术指标。计算机中原先的各种标准总线,例如ISA总线、EISA总线等已经无法满足现今计算机中高速率数据传输的要求。外围部件互连总线(即PCI)就在这种情况下应运而生。这是一种具备很高性能的32/64位局部总线,适应于计算机和外部设备之间的高速数据传输,并支持突发性数据传输。它已经迅速取代了计算机中原有的ISA总线,成为如今PC机中的主流总线。

PCI总线是一种同步的独立于处理器的32位或64位局部总线,最高工作频率为33MHz,峰值速度在32位时为132MB/s,64位时为264MB/s,总线规范由PCISIG发布。与ISA总线相比,PCI总线具有高速性、即插即用性、可靠性、扩展性和高速复用性等特点。论文网

随着PCI在计算机中的作用越来越突出,其设计的实现显得愈加重要。目前PCI的设计方法多种多样,有关基于FPGA的PCI总线接口设计也取得了一定的进展。为了更好地统一信息,加以规范,本次课题研究将所参阅的文献资料加以分类整理并提取有价值的信息,最终得出有效的结论。

1.2 PCI的研究现状

1.3 本文的主要内容

现如今,随着计算机技术的快速发展,PCI总线接口的开发已经成为一项非常重要的技术,目前也已经出现了多种设计方案。本文介绍了基于FPGA的PCI总线接口设计方案,利用Verilog HDL语言为工具,对PCI总线进行了描述,最后的结果也验证了设计方案的可行性。本文一共分为6章,具体安排如下:

第一章:PCI总线接口的研究背景

第二章:PCI概念、性能、总线命令等的基本介绍

第三章:Verilog HDL语言的介绍以及PCI系统架构的理解与划分

第四章:具体的Verilog HDL语言介绍

第五章:QuartusII软件进行仿真,并对仿真结果进行分析

第六章:对全文的总结

2 PCI总线概述

2.1 PCI总线的基本概念

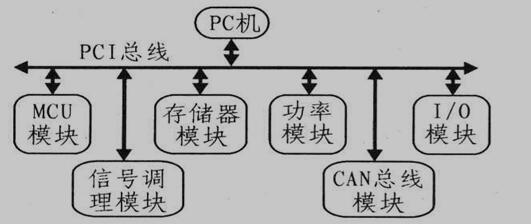

PCI总线从1992年创立规范到现今,已经成为计算机的一种标准总线,并取代了早先的ISA总线。PCI总线具有很多优点,比如即插即用、中断共享等。PCI总线模型如图2.1所示。

图2.1 PCI总线模型

PCI总线是由Intel公司于1991年推出的一种局部总线,局部总线(总线是计算机用来把信息从一个设备传输到另外一个设备的高速通道)英文全称是Peripheral Component Interconnection。从结构上来看,PCI是在CPU和原来的系统总线间插入的一级总线,并由一个桥接电路实现对这一层的管理,实现上下之间的接口以便协调数据的传送。管理器提供信号缓冲,使之能够支持10种外设,并能在高时钟频率条件下保持高性能。文献综述 VHDL+FPGA的PCI总线接口设计(2):http://www.751com.cn/tongxin/lunwen_74644.html