要注意的是,SCLK信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCLK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。也就是说,主设备通过对SCLK时钟线的控制可以完成对通讯的控制。SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。不同的SPI设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不同定义。

2.2 SPI传输模式

SPI有四种工作模式,各个工作模式的不同在于SCLK不同,具体工作由CPOL(时钟极性),CPHA(时钟相位)决定,当CPOL为0时,时钟空闲时候的电平是低电平,CPOL为1时,时钟空闲时候的电平是高电平;当CPHA为0时,时钟周期的前一边缘采集数据,CPHA为1时,时钟周期的后一边缘采集数据。

CPOL和CPHA分别可以为0或1,所以对应四种传输模式。如下图2.1 SPI四种传输模式所示:

图 2.1 SPI四种传输模式

SPI0传输模式,对应的CPOL为0且CPHA为0,此模式下,时钟空闲状态时为低电平,在串行同步时钟的第一个边沿(由于CPOL为低,因此第1个跳变沿只能为上升沿)开始进行数据采集;

SPI1传输模式,对应的CPOL为0且CPHA为1,此模式下,时钟空闲状态时为低电平,在串行同步时钟的第二个边沿(由于CPOL为低,因此第2个跳变沿只能为下降沿)开始进行数据采集;

SPI2传输模式,对应的CPOL为1且CPHA为0,此模式下,时钟空闲状态时为高电平,在串行同步时钟的第一个边沿(由于CPOL为高,因此第1个跳变沿只能为下降沿)开始进行数据采集;

SPI3传输模式,对应的CPOL为1且CPHA为1,此模式下,时钟空闲状态时为高电平,在串行同步时钟的第二个边沿(由于CPOL为高,因此第2个跳变沿只能为上升沿)开始进行数据采集;

这四种传输模式中比较常用的是SPI0模式和SPI3模式。每一种模式都与其他几种模式不兼容,实际应用中,SPI总线与外设进行数据通信时,需要根据实际情况来配置时钟SCLK的CPOL和CPHA产生不同的数据格式来满足不同的通信需求

本次设计中,采用时钟极性为0和时钟相位为0,也就是说,在SPI0传输模式下进行设计。

2.3 SPI协议

SPI协议是一个环形总线结构,其时序其实很简单,主要是通过时钟脉冲SCK控制两个寄存器交换数据。

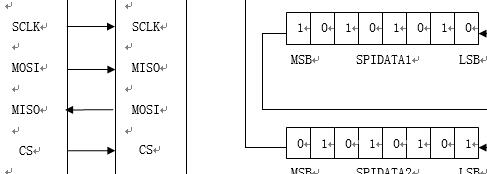

假设主机的 8 位寄存器 SPIDATA1 内的数据是待发送的数据10101010,从机的 8 位寄存器 SPIDATA2 内的数据是 01010101,遵循上升沿发送,下降沿接收,从高位到低位依次传送的规则,且两个寄存器之间以全双工方式进行通信。

图2.2 主、从机通信示意图

如图2.2所示,当第一个上升沿到来时,SPIDATA1 将最高位 1 移除,同时将所有数据左移,此时MOSI线上的电平为高。而SPIDATA2将最高位0移出,并将所有数据左移,此时 MISO线上的电平为低。然后,当该上升沿之后的第一个下降沿到来时,SPIDATA1 锁存 MISO 线上的电平并将其移入最低位,同样SPIDATA2 将锁存 MOSI 线上的电平,也将其移入最低位。

经过8个时钟脉冲后,两个寄存器完成了一次数据的交换。

通过下面的例子来示范一次完整的数据交换。 VHDL+FPGA的SPI通信接口设计(4):http://www.751com.cn/tongxin/lunwen_13593.html