直接频率合成的方法主要有相干直接频率合成法和非直接频率合成法。这两种实现方案最大的差异是基准频率的个数不一样。非相干频率合成法使用多个基准晶振进行频率变换,产生系统所需的频率。这种方法简单快捷,无用的镜像和杂散谐波较少,但同步性较差。相干直接频率合成法只使用一个基准晶振进行频率的变换。这种方法需要的倍频、谐波电路较复杂,但噪声小,同步性高。直接模拟频综方案整体的优势在于频率捷变、相噪较好、频稳度高,可是它的一个致命弱点是最终的频率合成系统体积庞大、机构复杂、故障率高。内部各种谐波、混频、倍频、滤波等模拟电路易受到外界信号的干扰。因此,这种纯模拟方法产生的频率合成器只能用于地面基站,不适合机动性高的应用场合。而且,正在逐渐淡出人们的视线。

近年来,由于微电子技术和集成芯片制作加工工艺的突飞猛进,单片模拟频率合成器已经面世并逐渐推广。这样便增加了直接频率合成器的便携性,拓宽了它的应用领域。

1.2.2 基于锁相环的间接频率合成技术

锁相环(Phase Locked Loop,PLL)是间接频率合成技术中的重要组成模块,它的基本模型就是一个相位负反馈控制环路,通过自动调节输出信号相位,使得输出信号与参考信号形成稳定的相差,这样完成了输出信号对参考信号相位的锁定,输出信号与参考信号的频率相等[7]。

基于锁相环的间接频率合成技术是在上世纪40年代左右受自动控制理论里的负反馈伺服环路模型启发发展起来的。锁相式间接频率合成技术和直接模拟频率合成技术类似,都要用到一个或多个基准晶振,通过混频、倍频、谐波、分频等电路处理,实现对基准频率的加减乘除。但PLL技术用锁相环来锁定需要的目标频率,抑制不需要的谐波和镜像杂散。即用锁相环取代了直接模拟频率合成技术中滤波器的功能。

基于锁相环的间接数字频率合成技术优点是用锁相环取代了一系列参数复杂的模拟滤波器,使得频率合成器的集成度高,易于调试和移植,通用性好。而且负反馈的原理使得输出频率的准确度和稳定度都很高。主要缺点就是频率分辨率不高、频率的锁定时间较长,跟踪频率变化时的延迟较大,由于倍频和大功率的VCO会引起相位噪声的恶化。

1.2.3 直接数字频率合成技术

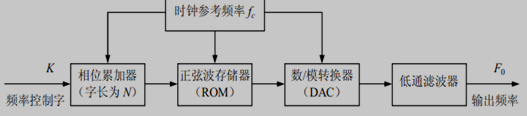

直接数字频率合成技术是一种新型的频率合成技术,与模拟频率合成技术的机理有着本质的区别,它是频率合成技术的一次[8]。70年代初,Tierney等人发表了关于新型数字频率合成器的研究成果[9],第一次提出了DDS概念。直接数字频率合成器的基本部件如图1.1所示。

图1.1 DDS原理图

在时钟参考频率的节拍下,将计算出的K位长度的频率控制字送入相位累加器中,相位累加器便以K为步长输出相位数据,然后把相位累加器输出的相位数据作为地址查询波形存储器[10]。波形存储器中存放的是相位与幅值的映射。波形存储器输出的数字波形幅值数据经过DAC转换成模拟信号波形,经过平滑滤波器将波形中的毛刺(高次谐波)滤除,最后可以得到DDS的输出频率[11]。

直接数字频率合成技术主要优点是可以实现信号源频率、幅度、相位改变的数字化,同时兼具相噪优良、频率间隔小、切换响应即时;主要缺点是工作频率有限,相噪及杂散相对比较差,信号质量不高,功率太小。

1.2.4 其他类型的频率合成技术

FPGA的DDS激励PLL相位可控信号源设计(3):http://www.751com.cn/tongxin/lunwen_72764.html