频综的性能需要一系列指标来表征,包括频率范围、频率分辨率、频率转换时间、频率准确度和稳定度、频谱纯度、系列化标准化及模块化的可实现性、成本体积及质量等等。

1.2 频率合成技术

实际频率合成设备通常采用以下三种技术:

1、直接频率合成技术,即DDS技术。其优点是响应快,缺点是成本高,且不能做到任意频率的合成,主要用于军事通信。

2、锁相环频率合成技术,即PLL技术。其优点是成本低,可合成任意频率,但是响应较慢,主要用于民用设备。

3、直接频率合成+锁相环频率合成技术,即DDS+PLL技术。结合上述两者优点,克服各种弊端。

频率合成技术,可以说是用一个或数个高频率稳定度的参考频率源,产生多个与参考频率稳定度相同或接近的新频率的技术。频率合成技术不但能提高通信频率和通信设备的稳定度、准确度,而且还能够满足通信自动化对频率可控与存储的要求,以及抗干扰对快速跳频的要求。源.自/751·论\文'网·www.751com.cn/

频率合成技术在毫米波步进雷达中有着及其典型的应用。雷达探测器是一种设计出来探测各个波段雷达波并使用声、光进行提示使用者的探测器。其中毫米波探测具有其显著的优点,例如精度高、抗干扰性能强、低仰角探测性能良好、有穿透等离子体的能力,而且用它设计出的探测器还具有设备体积小,结构紧凑,重量轻,频带宽、测距精度高,方向性好,多普勒检测能力良好,区别金属目标和周围环境的能力强等特点。在这些优点的基础上,设计出毫米波脉冲频率步进雷达频率合成器。

直接频率合成(DDS)是用混频器、倍频器和分频器实现频率间的加、减、乘、除来产生新频率,并靠滤波器选择使信号纯净。由于本文涉及不多,在此不为详述。

间接频率合成是用锁相环迫使压控振荡器 (VCO)的频率锁定在较高稳定的参考频率上,从中获得多个稳定频率,所以也被称为锁相式频率合成。由于锁相环路相当于一窄带跟踪滤波器,因此它能很好地选择所需频率的信号,抑制杂散分量,并且避免了大量使用滤波器,十分有利于集成化和小型化。此外,一个设计良好的压控振荡器具有较高的短期频率稳定性,而标准频率源具有较高的长期频率稳定度,锁相式频率合成器把这二者结合在一起,使其合成信号的长期稳定度和短期稳定度都很高。

1.3 FPGA简介

现场可编程门阵列FPGA和 CPLD(复杂可编程逻辑电路)都是高密度现场可编程逻辑芯片,都能将大量的逻辑功能集成于一个单片集成电路中,其集成度已发展到现在的几百万门。现场可编程门阵列FPGA是由掩膜可编程门阵列(MPGA)和可编程逻辑器件二者演变而未的,并将它们的特性结合在一起,因此FPGA既有门阵列的高逻辑密度和通用性,又有可编程逻辑器件的用户可编程特性。FPGA通常由接线资源分隔的可编程逻辑单元(或宏单元)构成阵列,又由可编程I/O单元围绕阵列构成整个芯片,其内部资源是分段互联的,因而延时不可预测,只有编程完毕后才能实际测量。文献综述

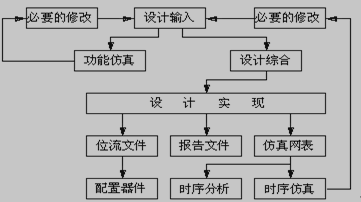

FPGA设计被分为设计输入、综合、功能仿真(前仿真)、实现、时序仿真(后仿真)、配置下载等六个步骤,设计流程如图1所示。下面分别简要介绍各个设计步骤。

FPGA频率综合器时序控制设计(3):http://www.751com.cn/tongxin/lunwen_72429.html

FPGA频率综合器时序控制设计(3):http://www.751com.cn/tongxin/lunwen_72429.html