3 开发板的模块电路设计

3.1 AT89C51单片机

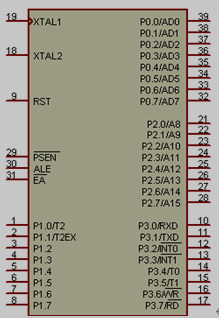

AT89C51是一种带4K字节FLASH存储器的低电压、高性能CMOS的8位微处理器,俗称即单片机。AT89C51是一种带2K字节闪存可擦除可编程只读存储器的单片机。单片机的可擦除只读存储器可以重复擦除1000次。该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89C51是一种高效微控制器。AT89C51单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。引脚排列所示图3-1所示。

图3-1 单片机引脚图

由于电路原理中只用到单片机的p0、p1、p2口,所示下面对这三个端口进行详细介绍。

P0口:P0.0~P0.7统称为P0口,在不接片外存储器与不扩展I/O接口时,作为准双向输入/输出接口。在接有片外存储器或扩展I/O接口时,P0口分时复用为低8位地址总线和双向数据总线。P0口是一个三态双向口,由一个输出锁存器、两个三态缓冲器、输出驱动电路和输出控制电路组成。在输入数据时,应人为地先向P0口写“1”,定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的低八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1.0~P1.7统称为P1口,可作为准双向I/O接口使用。P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4LSTTL门电流。P1口管脚写入“1”后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是因为内部上拉。

P2口:P2.0 ~P2.7口统称为P2口,一般可以作为准双向I/O接口使用,在接有片外存储器或扩展I/O接口且寻址范围超过256字节时,P2口用作高8位地址总线。P2口是一个内部上拉电阻的8位双向I/O口,P2口的缓冲器可以接收,输出4个TTL门电流,当P2口为“1”时,管脚被内部上拉电阻拉高,并且作为输入。当其作为输入时,P2口的管脚被外部拉低,因此将会输出电流。这是因为内部上拉的缘故。当P2口用于外部程序存储器或者是16位地址外部数据存储器进行存取的时候,P2口的输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

3.2 单片机外围电路

时钟电路是产生单片机工作时所需要的时钟信号,时序是指令执行时各信号间的相互关系。 单片机本身就作为一个复杂的同步时序电路, 为了确保同步工作方式的实现, 电路应确保在唯一的时钟信号控制下严格地按时序进行工作。

在本次设计中,时钟电路设计就是采用内部方式,即利用芯片内部的振荡电路。AT89C51单片机内部有一个构成振荡器的高增益反相放大器。引脚XTAL1和XTAL2分别是高增益反相放大器的输入端和输出端。高增益反相放大器将和片外晶体谐振器一起构成一个自激振荡器。片外接晶体振荡器以及电容C4和C5构成并联谐振电路,置于放大器的反馈回路之中,虽然对于外接电容的值没有太多的要求,但电容的大小会影响振动速度和温度的稳定性,振动频率的高低以及振荡器的稳定性。因此,此系统电路的晶体振荡器的值为12MHz,电容应尽可能的选择陶瓷电容,电容值约为22uF。在焊接刷电路板时,我们应注意晶体振荡器和电容尽可能安装的与单片机芯片靠近些,用以减少寄生电容,为了更好地确保振荡器可靠地工作和稳定行 AT89C51单片机实验开发板设计+电路图+程序(4):http://www.751com.cn/zidonghua/lunwen_74608.html