它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆将代码传送到目标芯片中,实现设计的数字系统。经过几十年的发展,许多公司都开发出了CPLD可编程逻辑器件。比较典型的就是Altera、Lattice、Xilinx世界三大权威公司的产品。

1.3 本文研究背景和主要内容

电子技术迅猛发展,高新技术日新月异。传统的设计方法正逐步退出历史舞台,取而代之的是基于EDA技术的芯片设计技术,它正在成为电子系统设计的主流。大规模的可编程器件现场可编程门整列FPGA和复杂可编程逻辑器件CPLD是当今应用最广泛的两类可编程专用集成电路。其性能好、可靠性高、容量大、体积小、微功耗速度快、使用灵活、设计周期短、开发成本低、静态可重复编程、动态在系统重构、硬件功能可以像软件一样通过编程来修改,极大提高了电子系统设计的灵活性和通用性。电子工程师和科学研究人员利用该类器件可以在办公室或者实验室设计出所需要的专用集成电路,大大缩短了产品的研发周期和降低成本。近年来,可编程逻辑器件的开发生产和销售规模以惊人的速度增长,且广泛地应用于航空航天、网络通信、军用雷达、仪器仪表、工业控制、医用CT、家用电器、手机和计算机等各个领域。它的广泛应用,使传统的设计方法在进行一场巨大的变革。

CPLD的各种功能块是通过Verilog HDL语言实现的。测频仪器性能各不相同,将CPLD的高速高可靠性和等精度测频原理较高的测量精度相结合,具有速度快、功能全、精度高等特点。

本文所作的具体工作如下:

(1)通过对各种参考资料的整合,了解了频率测量技术的需求及其应用前景。整理出多种频率测量方法及其原理,可实现性和优劣,进行比较后,选定多周期同步等精度的测量方法,并对其作出详细描述。

(2)了解CPLD发展现状,对其设计方法有一定的认识。大致了解本文所用的目标板的硬件结构及实现功能,在实验室环境下,对整形部分电路进行调试,观察得到预期效果。

(3)学习完硬件后要对软件进行熟悉。学习Quartus Ⅱ软件的基本功能,包括程序编写,程序编译以及仿真等功能。熟悉Verilog HDL语言描述能力。

(4)以上准备工作完成后,在Quartus Ⅱ软件中进行程序的编译调试和仿真。最终得出仿真波形图,并分析。

2 方案设计

2.1 测量原理

2.1.1 直接测量频率的原理

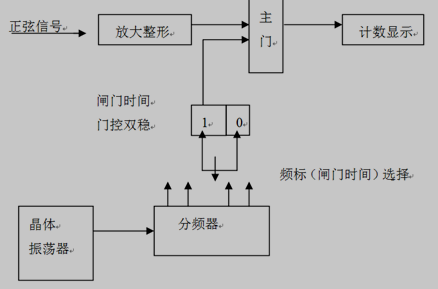

无论频率、周期还是时间间隔的测量,均是基于主门加计数器的结构而实现的,这种计数式直接测频的原理框图如图2.1所示。

图2.1 计数式测频的原理方框图

其中主门具有“与门”的逻辑功能。主门的一个输入端送入的是频率为fX窄脉冲,它是由被测信号经A通道放大整形后得到的。主门的另一个输入端送入的是来自门控双稳的闸门时间信号TS。因为门控双稳是受时基(标准频率)信号控制的,所以TS既准确又稳定。设计时通过晶体振荡器和分频器的配合,可以获得10s、1s、0.1s等闸门时间,由于主门的“与”功能,它的输出只有在闸门信号TS有效期间才有频率为fX的脉冲输出,并送到计数器去计数,计数值为N=TS = TS·fX,它与被测信号的频率fX成正比,有此可得: CPLD测量频率的电路与软件(3):http://www.751com.cn/wuli/lunwen_65502.html