研究背景及研究意义

数字频率计是电子测量领域最重要最基本的测量仪器之一。传统的数字频率计多 采用专门的计数芯片和数字逻辑电路组成,这样的频率计虽然结构简单,但是因为计 数芯片的工作频率不高,所以限制了频率计的工作频率,往往不能满足一些需要测量 很高频率的场合,而频率计的精度也受到芯片的很大影响。

针对传统频率计存在的弊端,本课题研究了了一种基于单片机和 CPLD 的数字式 频率计,该频率计采用等精度测量,改善了测量精度随着信号频率的变化而变化的问 题,测量精度得到了提高。同时,系统将单片机的控制灵活性及 CPLD 芯片的现场可

编程性相结合,不但大大缩短了开发研制周期,而且使本系统具有结构紧凑、体积小, 测频范围宽、可靠性高,精度高等优点。本课题在 FPGA/CPLD 技术越来越成熟,应用 越来越广泛的情况下来实现等精度数字频率计,具有重大的意义。

1.4 本课题的主要内容

本课题介绍了频率计的概念、发展及研究概况,讲述了测量频率的几种方法和比 较;单片机部分 STC89C52RC 功能及引脚概述、CPLD 模块概述、Quartus II 简单介 绍、VHDL 硬件描述语言、单片机与 CPLD 接口电路设计等,最后论述了软件部分设计 与仿真包括单片机部分汇编语言编写与调试、CPLD 部分用 VHDL 语言实现的计数器设 计、仿真与分析等。 在研究本课题的过程中,笔者做了以下几项工作:

(1)笔者对查阅了相关课题的资料,学习并整理了前人的研究成果,在自己研究的 过程中借鉴前人的方法,改进不足的地方。在笔者看来,查阅并学习文献是所有研究 的基础。

(2)硬件电路的学习。虽然本课题中不需要自己设计电路,降低了课题的难度,但 是仍然需要学习硬件电路的一些基本知识、编程语言以及一些注意点等。

(3)CPLD 部分使用 VHDL 语言编写程序,在 Quartus II 7.0 环境进行调试与仿真, 然后绘制原理图并进行仿真。

(4)单片机部分采用 C 语言编写,在 Keil 软件中进行调试。

2 系统设计原理

频率就是单位时间所含被测信号周期的个数,因此测频的基本原理就是测量给定 时间内被测信号的重复次数。测频的方法主要有直接测频法和等精度测频法,直接测 频法为传统的测频法,测频误差大、测频范围窄等缺点限制了其应用与发展,而等精 度测频法是基于直接测频法发展起来的,它正好克服了直接测频的缺点,从而在较宽 的频率范围内具有较高且相等的测频精度,因此在测频系统中具有广泛的应用前景, 下面具体介绍这两种测频方法。

2.1 直接测频法

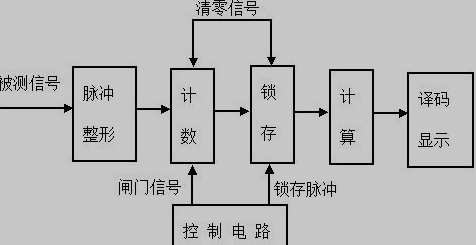

直接测频的基本思路就是在给定的闸门时间内对未知信号进行计数,直接测频可 以按照被测信号频率高低的不同分为两种情况。如下图 2.1 所示为直接测频的测量原 理框图。

图 2.1 直接测频原理框图

(1)被测信号频率较高时

此时,闸门信号周期大于被测信号周期,被测信号在闸门宽度 T 内进行计数,计 数值为 N,因此被测信号频率为:

STC89C52RC单片机和CPLD的等精度频率计(3):http://www.751com.cn/tongxin/lunwen_76975.html