被测单元需要高速采集的信号,经过输入调理电路完成信号的滤波、单端到差分转换后提供给双路高速ADC。在进行信号采集、存储之前,通用测试平台通过RS-232串行接口发送高速采集的采样频率、采集长度等参数给专用适配器的嵌入式ARM CPU,ARM CPU接收到采集相关的参数后,通过与FPGA的总线接口将参数传给FPGA,这样通用测试平台就可以启动高速采集、存储操作了。通用测试平台通过1位数字输出产生正脉冲信号启动信号采集,FPGA将高速ADC转换的16位数据存储到FPGA外扩的高速同步突发存储器(SSRAM)中,当采样长度达到通用测试平台设置的采样点数后,FPGA产生中断信号通知ARM CPU读取采集数据,CPU读取SSRAM中的采样数据后通过RS-232接口输送给通用测试平台的主控计算机,由主控计算机对采集的信号进行分析、处理。系统扩展1M*36bit的SSRAM存储器,在最高100MSPS的采样速率下,每个通道可以存储10ms的信号波形,这些可以满足雷达被测单元的测试要求。

2.2 总框架图及设计指标

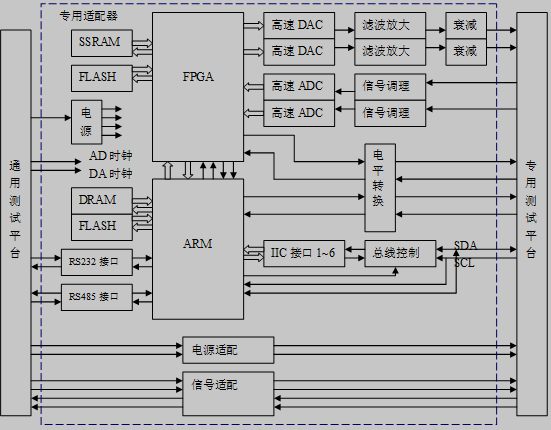

图2.1 适配器设计的框架图

1)DAC产生信号路数:2路。

DAC转换速率:≥100MSPS;分辨率:12位。

输出信号最大峰峰值:≥2V;输出阻抗:50Ω。

2)输出信号的衰减量≥40dB。

3)高速采集信号路数2路。

4)高速ADC转换速率:≥100MSPS;分辨率:16位。

5)存储容量每通道≥1MByte。

6)触发方式外触发(由通用测试平台的高速数字输入输出信号提供)。

7)通信接口RS-232接口;网络接口。

8)供电+12V、+6V、-6V供电电源由通用测试平台提供;功耗:≤10 W。

FPGA+ARM故障检测设备专用适配器硬件设计(3):http://www.751com.cn/tongxin/lunwen_72904.html