(1)对系统的总体设计方案的阐述,系统流程图。

(2)基于DM642的硬件平台的上手操作机了解。主要DM642的性能的了解,包括对其主要特征性能的研究,以及对实验室现有的DM642硬件平台的上手。

(3)基于CSS2.20的软件设计,针对实验室现有的DM642硬件实验平台进行软件设计,实现图像输入,在硬件系统内进行编码,处理,解码,最后输出的过程,达到图像采集的目的。

(4)在实验室进行程序验证,通过实验室现有的硬件平台进行硬件连接进行图像采集,来验证程序的正确性。

2 整体设计方案

2.1设计目标

设计目标主要集中在软件方面,在熟悉了解硬件系统以及现有的实验模板上进行程序的设计,在硬件连接的基础上并完成实验程序的验证。

2.2 系统整体的设计方案

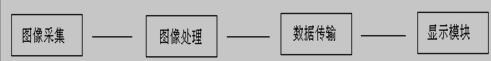

一个完整的的图像处理系统通常是由多个部分组成的,但一般来说分为4个部分:图像采集、图像处理、数据通讯和显示模块,如图2.1所示。

图 2.1 图像系统组成

而本文主要讨论的是图像采集模块。由于不涉及图像处理,本系统的主要目的是将图像由固定制式(PAL或NSTC制式)的摄像头输入,在信号经过视频解码芯片解码成数字并行信号BT656码流送至DSP进行储存,便于图像处理,由于是一个完整的系统,最后仍然要将未处理的图像从储存器中进行编码最后输出。 图像采集模块的

图像采集模块,最主要的功能是负责图像的获得和进行解码,所要采集的图像信息会被传感器(例如CCD和CMOS)所采集并被转化成对应的电信号。之后这些模拟电信号经由专门的解码芯片完成解码过程以适应PAL,NTSC等多种信号源的输入。用的SAA71为4例,在SAA714内部拥有两个模拟预处理通道,可以完成对视频信号的可编程自动增益控制;CVBS、Y和C的自动籍位控制;50HZ和60Hz场频率的自动探测以及PAL和NTSC标准的自动转换。其数据采集通道带宽为8位或16位,在缩放后以4:2:2、4:l:l、4:2:0或4:z:0的YUV格式输出。其解码过程通常是由I2C总线来控制的。源:自~751·论`文'网·www.751com.cn/

I2C总线是一种常用的解码芯片串行数据传输总线,其包含SDA和SDC两条线,可以实现完备的全双工同步数据传输,最高传送速率可达100Kbps。I2C总线在传送数据过程中有开始、结束和应答信号这三种信号。开始信号指SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据;结束信号指SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。应答信号则指:接收数据的IC在接收到8bit/l6bit数据后,向发送数据的IC发出特定的低电平脉冲,表示已收到数据。CPU向受控单元发出一个信号后,等待受控单元发出一个信号,CPU接收到应答信号后根据情况做出是否继续传递信号的判断。图2.3表示了一个8bit情况下的I2C工作过程。在产生开始信号后,CPU发出受控单元的地址,在接受到来自受控单元的应答信号(ACK)后,CPU将数据信号发送给受控单元。I2C总线将会在接受到结束信号后结束此次操作。

高速DPS数字图像处理平台采集程序设计+程序(3):http://www.751com.cn/tongxin/lunwen_72081.html