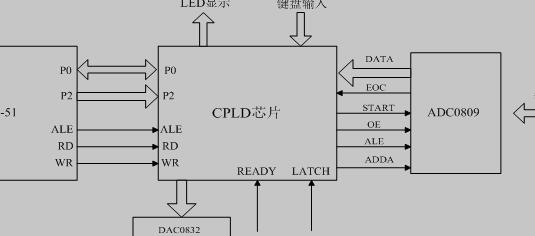

图2.1 CPLD系统接口电路图

CPLD在集成开发软件平台上进行编程,编程方式主要有文本设计、原理图设计、波形设计等。其中文本设计比较灵活方便,常见的文本编程语言为Verilog HDL语言、AHDL语言、VHDL语言,这三种硬件描述设计语言被广泛应用于各种硬件设计中,本文所介绍的就是一种用Verilog HDL语言编程实现铁电存储器功能的方法。CPLD采用在系统编程技术,极大的方便了硬件调试与修改,当发现设计有问题或者要对芯片进行其它设计时,直接修改原理图或者硬件描述语言就可以了,批量生产时只需将代码复制到其它CPLD芯片中。CPLD的设计流程为打开QuartusII软件→用Verilog HDL语言编程→编译→写测试脚本,进行仿真,验证仿真结果→设置输入输出管脚→生成代码→将代码通过下载电缆存储在CPLD芯片中。它具有设计制造成本低、集成度高、编程灵活、适用范围宽、开发周期短、保密性强、对设计者的硬件经验要求低等优点,因此被广泛应用于汽车电子、仪器仪表、航天测控设备、数控机床等产品的原型设计和产品改进之中[19]。

2.2 FPGA特点及简介

FPGA(Field-Programmable Gate Array)现场可编程门阵列的出现是超大规模集成电路和计算机辅助设计发展的结果,1985年Xilinx公司生产出第一款FPGA芯片,它是由GAL、CPLD、PAL等可编程器件发展而来的产物,它的出现既解决了可编程器件门电路有限的问题,又克服了定制电路的一些缺点[20]。通过硬件描述语言完成电路设计,经过综合与布线布局之后烧录至FPGA芯片上进行测试,已成为现代IC设计验证的主流技术。

FPGA芯片主要由输入输出模块IOB、可配置逻辑模块CLB、内嵌的专用硬件单元、内嵌底层功能单元、嵌入式块RAM和内部连线751部分组成。FPGA的IOB模块是可编程的,IOB模块包含可编程缓冲器、存储器、可编程延时线等,用户可根据实际需要对输入输出单元进行编程,以满足不同电器特性对不同输入/输出的匹配;可配置逻辑模块是FPGA基本的逻辑单元,每个CLB模块都由几个互连的宏块条和开关矩阵组成[21]。内嵌的专用硬件单元,其具有ASIC电路的功能,一些FPGA集成了专用乘法器,一些高级FPGA中还集成了串并收发器;内嵌底层功能单元包括DSP、CPU、DLL等软处理核,这大大增强了FPGA的功能,使之成为系统级设计工具[22]。嵌入式块RAM可以配置成双端口RAM、单端口RAM、FIFO和内存地址存储器等常用的存储结构,用户可以根据需要选择不同的存储深度和位宽;FPGA芯片中的各个模块通过其内部丰富的布线资源进行连接,其内部共有四类布线资源:短线布线资源、长线布线资源、分布式布线资源和全局布线资源,设计软件会自动根据网表来分配布线资源[23]。与CPLD不同,当系统掉电后,FPGA内部逻辑关系消失,具有掉电易失性。

2.3 CPLD和FPGA的主要区别

虽然CPLD和FPGA都是可编程ASIC器件,两种芯片有很多相似的地方,但由于CPLD和FPGA结构上的差异,其仍有很多不同点:

1、CPLD的运行速度比FPGA快,而且由于其逻辑块之间采用集中式布线结构,所以其具有较大的时间可预测性;而FPGA采用了分布式布线结构,所以无法预测其延迟。

2、CPLD主要采用FASTFLASH或E2PROM技术编程,可以进行上万次编程,系统掉电时编程信息不丢失;FPGA是基于SRAM编程的,系统掉电时编程信息会丢失,系统上电时需要将编程信息重新写入SRAM中,其优点是可以实现快速编程和无限次编程[18]。

3、CPLD 比FPGA使用起来要方便,对于CPLD ,通常只要触发器数目、内部门和输入输出端口数不超过芯片的资源并有一定余量,就可以达到设计要求;而对于FPGA ,因为无法确定完成设计所需要的CLB 逻辑级数,所以只有经过多次试验才能得到满意的结果[24]。 基于CPLD的弹载数据存储器的设计+Modelsim仿真(3):http://www.751com.cn/jixie/lunwen_22835.html