国际标准的TCP/IP得到了广泛的应用,成为计算机通讯事实上的国际标准,是Internet最基本的协议。

TCP/IP是一个四层的体系结构,由下至上依次是网络接口层、网络层、传输层、应用层。

网络接口层对应的是网络的硬件部分,包含ARP协议和RARP协议,是Internet的物理构成,包括设备驱动程序和网卡接口等,处理传输媒介的物理接口细节。

网络层定义了互联网传输的报文的格式,处理来自传输层的分组发送请求,处理输入数据报,处理路径、流控、拥塞等问题,包含IP协议、ICMP协议和 IGMP协议。

传输层为主机上的应用程序提供端到端的通信,包含TCP协议和UDP协议。

应用层处理特定的应用程序细节,包括 HTTP协议、FTP协议等。

2.3本章小结

本章介绍嵌入式TCP/IP协议栈的相关知识,简单分析了目前比较流行的嵌入式操作系统作,深入分析了Cortex-M3内核,也分析了TCP/IP协议桟的体系结构。

第3章 μC/OS-II在ARM上的移植

3.1 LM3S8962嵌入式微处理器

LM3S8962是一款基于ARM cortex-M3内核的微控制器,是专业针对工业应用方案设计的,可用于工业自动化,运动控制以及网络设备和交换机等。LM3S8962具有一个电池备用的休眠模块,可用于对功耗有特别要求的场合。LM3S8962的管脚如图3.1所示:

图3.1:Lm3s8962管脚图

LM3S8962-EVM开发板的实体图以及板上的硬件资源如图3.2所示:

图3.2

* lm3s8962具有32位risc性能

--采用为小封装,基于ARM cortex-M3 v7架构

--提供系统时钟,一个简单的24位写清零,递减,自装载计数器,控制机制灵活

--THumb-2指令,具有较高的代码密度

--工作频率为50MHz

--硬件除法,单周期乘法

--集成嵌套中断向量控制器

* 内部存储器

--256kb的Flash存储器

* 通用定时器

--具有4个通用定时器模块,每个提供2个16位的定时器,可以被独立配置

* 10/100以太网控制器

--符合IEEE 802.3-2002规范

--遵循IEEE 1588-2002精确时间协议(PTP)

--集成10/100mbps收发器

--节能与断电模式

--可编程的MAC地址

* UART

-- 两个独立可编程的UART

--带有独立的16*8发送(TX)以及16*12接受(RX)FIFO

* I2C

--中断的产生

--支持端个主机以及7位地址模式

* PWM

--3个 PWM信号发生模块,每个模块都带有1个16位的计数器,2个比较器,1个 PWM信号发生器以及一个死区发生器

3.2 μC/OS-II的简介与体系结构

实时系统的特点是,如果逻辑和时序出现偏差,将会引起严重后果。有2种类型的实时系统:软实时系统和硬实时系统。

在软实时系统中,系统的宗旨是使各个任务尽快地运行,而不要求限定某一任务在多长时间内完成;在硬实时系统中,各任务不仅须执行无误,而且要做到准时。

大多数实时系统是二者的结合。实时系统的应用涵盖广泛的领域,而多数实时系统又是嵌入式的。这意着计算机建在系统内部,用户看不到有个计算机在系统里面。

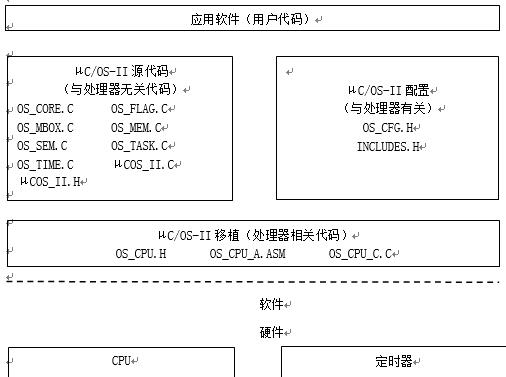

μC/OS-II的体系结构及它与系统硬件的关系如图3.2所示。

图3. 2 μC/OS_n的体系结构

3.3 μC/OS-II 的移植

3.3.1 μC/OS-II 移植要求

移植是通过修改内核代码,以便它可以运行在其他处理器或控制器。正常运行μC/OS-II应该具备如下条件: 基于Ctex-M3 ARM的TCP IP协议栈的设计与实现(4):http://www.751com.cn/jisuanji/lunwen_15018.html